本文来自微信公众号“魔铁的世界”。

5nm是EUV(极紫外线)光刻机能实现的目前最先进芯片制程工艺,也是智能手机厂商争抢的宣传卖点,进入2020年下半年后,苹果A14、麒麟9000、骁龙888等5nm工艺芯片相继粉墨登场。

然而,公开的信息显示,无论A14、麒麟9000,还是骁龙888,均被曝出芯片的实际功耗发热与厂商宣传的美好相差甚远,一时间,“5nm芯片集体翻车”的话题成为网络热点。

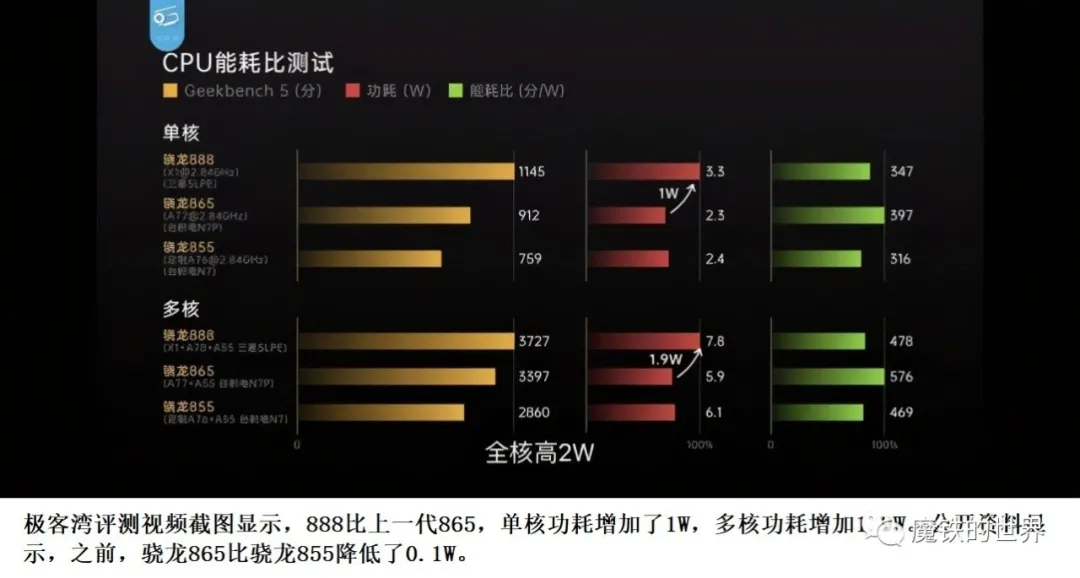

骁龙888功耗等于低压酷睿?根据AI财经社的报道,5nm芯片最让人诟病的,是性能虽然有所提升,但功耗却比7nm的明显增加,这其中表现最差的就是骁龙888,被调侃为“火龙888”。数码评测媒体极客湾对骁龙888、骁龙865、骁龙855测试的功耗数据表明,单核功耗上,骁龙865最低,为2.3瓦,其次是骁龙855的2.4瓦,骁龙888最高,达3.3瓦,相比骁龙865高了1瓦,高出幅度达43.5%。多核功耗方面,最低的依然是骁龙865,为5.9瓦,其次是骁龙855的6.1瓦,骁龙888依然落在最后,功耗高达7.8瓦,是骁龙865的1.32倍。具体见下图。

骁龙888多核功耗高达7.8瓦是个什么概念?英特尔第11代低压酷睿i7处理器的功耗在7——15瓦,可用于超轻轻薄笔记本电脑(在无风扇散热时,功耗锁定为7瓦)。也就是说,骁龙888的多核功耗已经相当于一颗第11代低压酷睿i7处理器,但需要明确的是,低压酷睿i7处理器采用的是10nm工艺制程,落后台积电、三星的5nm不少。

英特尔处理器采用复杂指令集,理论上相比采用精简指令集的骁龙888更为耗电,但骁龙888在占据工艺先进至少一代的优势下,功耗竟然相当于英特尔低压酷睿。不知道英特尔看到这里会是什么心情。骁龙888功耗猛增,最直观的体验就是,手机如果运行较大型的游戏,发热就比较明显。

极客湾的数据表明,在某款游戏的测试中,玩了20分钟后,小米11背面温度达到了48℃,而搭载骁龙865的小米10在相同的测试环境下,温控表现更好只有41℃。爱范儿对搭载A14芯片的iPhone12运行《原神》游戏测试表明,20分钟后,手机背面最高温度达到47℃,接近小米11。5nm的芯片在制程工艺上更先进,为何功耗表现却落后于7nm的芯片?答案是和芯片内部的晶体管漏电有直接关系。

为何晶体管漏电是元凶?A14、骁龙和麒麟等手机SoC芯片属于数字集成电路,而随着制造工艺的不断进步,集成电路的功耗越来越复杂,但总体可分为电路逻辑状态转换产生的动态功耗,以及CMOS晶体管各种泄露电流产生的静态功耗(又称漏电流功耗)。在芯片进入深亚微米工艺时代之前,动态功耗一直是芯片设计关注的焦点,但在进入深亚微米工艺时代之后,动态功耗在总功耗中的比例越来越小,静态功耗的比例则越来越大。

当芯片制造工艺进入纳米时代后,漏电流功耗对整个功耗的影响已经变得非常显著。有研究表明,在90nm工艺的电路中,静态功耗可以占到总功耗的40%以上。

究其原因,是因为集成电路每一代制造工艺的进步,都是以缩短CMOS晶体管的沟道长度为目标,7nm工艺指的就是指沟道长度。沟道长度不断缩短,使得电源电压、阈值电压、栅极氧化层厚度等工艺参数也在不断地按比例缩小,直接导致短沟道效应(SCE)、栅极隧穿电流、结反偏隧穿电流等漏电流机制越来越显著,表现为芯片漏电流功耗不断上升。

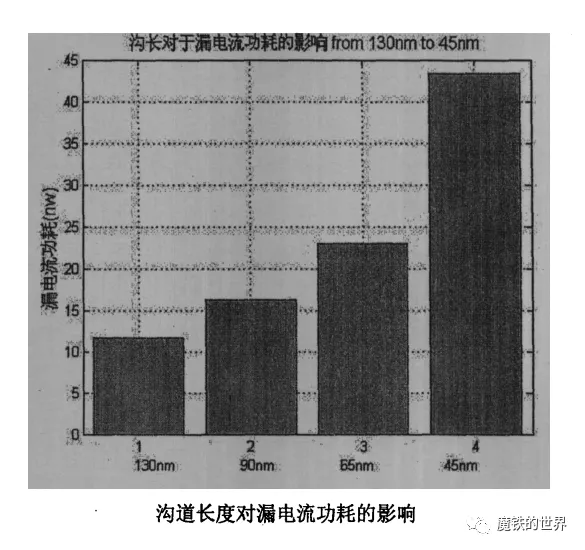

有研究表明,当晶体管的沟道长度从130nm缩短到90nm时,即缩小30.77%,漏电流功耗上升大约39.25%,但缩短到45nm,即缩小65.4%时,漏电流功耗上升大约273.28%(具体见下图)。

也就是说,漏电流功耗和缩小的沟道长度之间不是简单的比例关系,即使沟道长度缩短一点,漏电流功耗也会有一个数量级的增长,而且随着沟道长度越来越短,漏电流功耗增长越来越快。如果复盘芯片制造历史,会发现漏电流功耗曾长期困扰英特尔、三星和台积电等制造大厂。台积电为何被称台漏电?长期以来,芯片制造大厂一直在和漏电流功耗作斗争,每有进展,都是值得大书特书的新闻,比如英特尔。

相反,台积电2010年刚推出28nm工艺制程时,由于技术不成熟,漏电流功耗高,导致芯片的功耗大到难以接受,被市场调侃为“台漏电。”有长达6年时间,都摘不掉这顶帽子。

在当时,如何压制漏电流功耗几乎可以决定芯片工艺制程赛道上选手的身位。彼时,英特尔还是制造技术大拿,率先通过Gate-last技术压制了漏电流功耗,台积电则走了一些弯路,沿用IBM的Gate-first 技术,但效果不佳,在28nm上栽了跟斗,后在蒋尚义的主导下,改走英特尔Gate-last技术路线,才算解决漏电流功耗过高难题。

2011年第4季度,历经波折后,台积电终于量产成熟可靠的28nm制程。三星本来在32纳米制程也采用Gate-first

技术,但后来在28 纳米制程时,快速切换到Gate-Last 路线,之后的14纳米也基于Gate-Last。

据说,三星是通过梁孟松解决漏电流功耗问题,成功缩短与台积电的工艺差距。结果引发台积电起诉梁孟松,迫使后者离开三星半导体,辗转到中芯国际。由此可见,压制晶体管漏电流功耗有多重要。

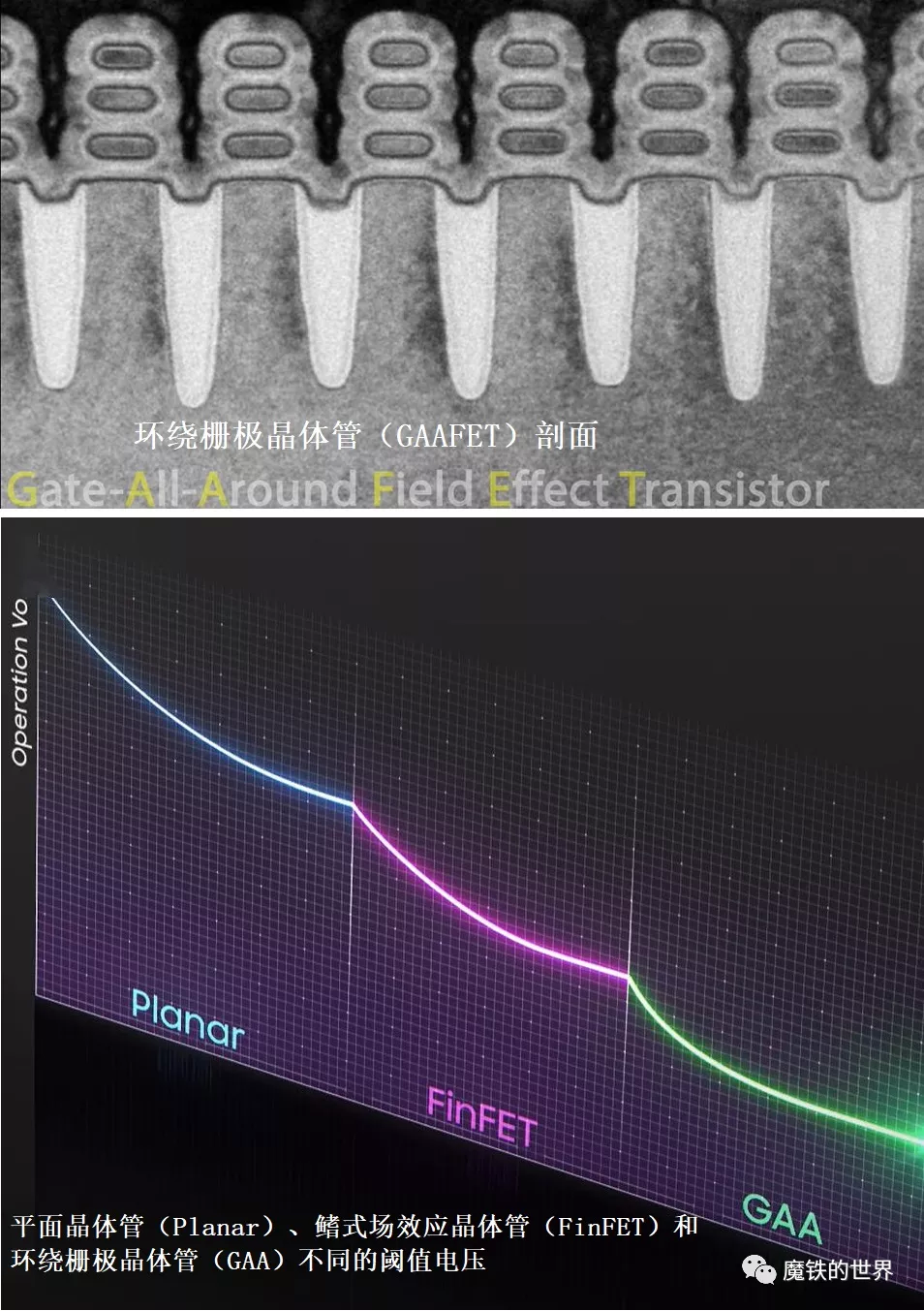

为何老迈的技术不退休?台积电、三星和英特尔之所以能压制漏电流功耗问题,主要原因是采用了创新的鳍式场效应晶体管(简称FinFET,见附图),以替代传统的平面式晶体管。

但由加州大学伯克利分校胡正明教授发明的鳍式场效应晶体管(FinFET),通过局部技术改良,从28nm工艺制程一直沿用至今,可谓发挥到了极限。

随着制程工艺进入EUV时代,漏电流功耗重新成为挑战。在7nm时,老迈的鳍式场效应晶体管(FinFET)技术就应该谢幕了,由环绕栅极晶体管(GAAFET)接替。

但由于技术风险和成本压力,大厂们在5nm时代仍不得不使用老迈的鳍式场效应晶体管(FinFET)技术,结果就是如前文所述,5nm的芯片漏电流功耗飙涨,在功耗上集体翻车,几乎消耗掉制程工艺进步的红利。也可以看出,芯片制造技术每往前跨一步,其实都极为不易。

那么,鳍式场效应晶体管(FinFET)会应用到什么时候?从公开的信息看,英特尔计划在5nm(接近台积电3nm工艺)时切换到环绕栅极晶体管(GAAFET),台积电则计划3nm之后再说,三星为了追平与台积电的工艺差距,决定豪赌一把,抢先台积电一步,在3nm时就采用环绕栅极晶体管(GAAFET)。总之,在环绕栅极晶体管(GAAFET)正式撸起袖子上阵之前,芯片的发热仍然会是一个问题。

(编辑:玉景)